MOSFET Basics

School of Electronics & Computing Systems

UNIVERSITY OF Cincinnat

# 6.1– Transistor Operation 6.4.1 & 6.4.2 MOSFET Basics

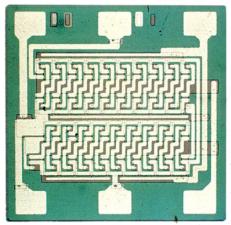

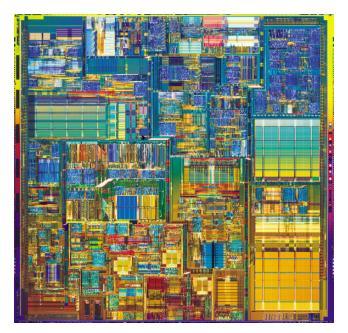

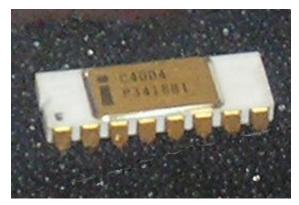

Images for this lecture: 1<sup>st</sup> MOS IC (RCA, 1964), 1<sup>st</sup> commercial microprocessor (Intel 4004, 4 bit, 2,300 transistors, 92 kHz, \$60,1971), and a modern chip...

No other human artifact has been fabricated in larger numbers than MOSFETs!

SECS 2077 – Semiconductor Devices ©

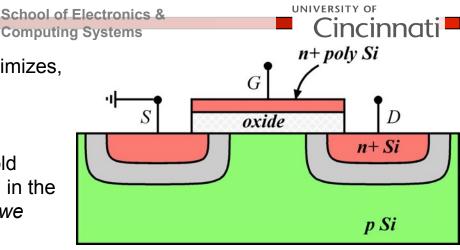

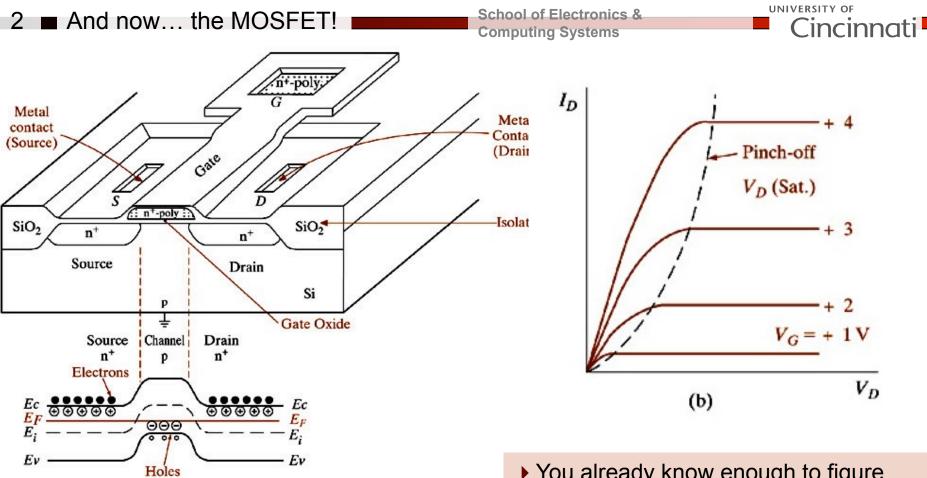

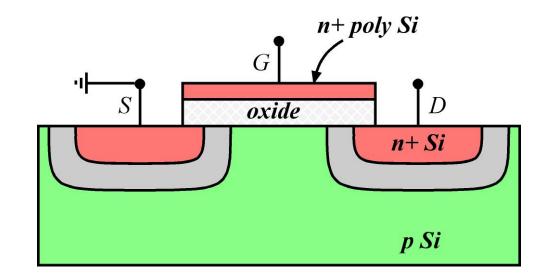

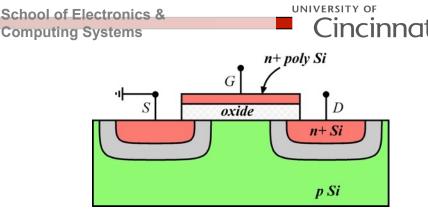

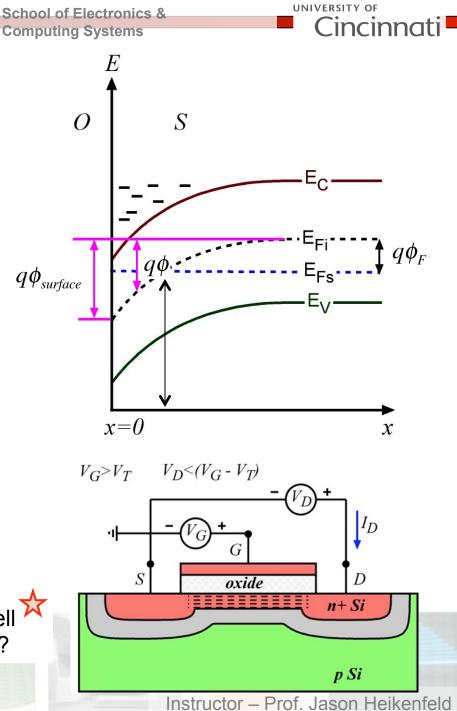

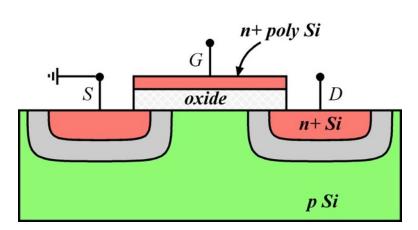

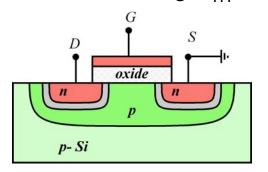

#### **FABRICATION**

- Substrate light doped p-Si

- n+ source/drain (diffused)

- thermal oxide (SiO<sub>2</sub>)

- n+ poly-Si gate electrode (thermally stable and best adhesion to oxides)

- metal contacts (apertures)

- thick isolation oxide

SECS 2077 – Semiconductor Devices ©

You already know enough to figure this out! So, tell me right now, why can't we get current flow from source to drain?

If we applied voltage to gate turn on, + or - ? Why?

The MOSFET...

3

n+-poly G Metal Metal contact Contact (Source) (Drain) Gate D S n\*-poly :? -Isolation SiO<sub>2</sub> SiO<sub>2</sub> n<sup>+</sup> n<sup>+</sup> Source Drain Si p Ť Gate Oxide Source Channel Drain n+ n<sup>+</sup> р Electrons  $\oplus \oplus \oplus \oplus \oplus$  $\oplus \oplus \oplus \oplus$ EF 000 Ev Ev

## **OPERATION**

Fermi levels flat in equilibrium

UNIVERSITY OF

Jincinno

Built-in barrier forms and prevents electron conduction in channel... (back to back PN' s!)

Apply positive voltage, push bands down, provide a conductive channel for electrons to travel in...

MOSFET TYPES:

(1) Enhancement mode nchannel device (at left) ...normally OFF

(2) Depletion mode ...normally ON

Instructor – Prof. Jason Heikenfeld

SECS 2077 – Semiconductor Devices ©

Holes

4 Basic Operation

Cincinnati

Unbiased device (floating contacts)

Depletion regions formed between n+ and p, why n+? Two reasons...

► Now, even if we applied bias between drain and source these back-to-back diodes would prevent current flow

► So what is our ONLY option to get current flow from source to drain? Need to change the channel... We need to create lots of electrons in the channel (n-type!).

What if we reversed all the doping types?

► If you can answer these questions then you are well on your way to understanding basic MOSFET principles!

SECS 2077 – Semiconductor Devices ©

5 Basic Operation

School of Electronics & Computing Systems

Cincinnati

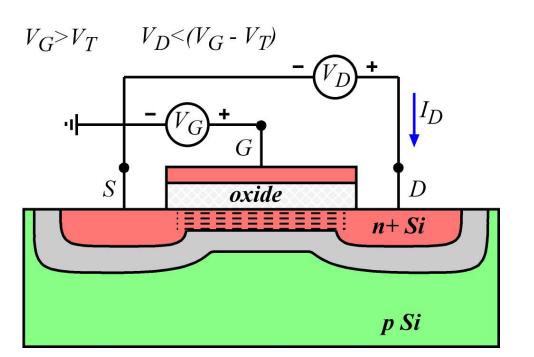

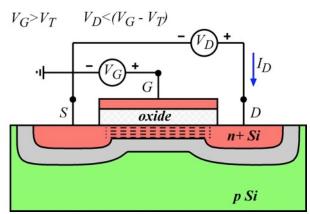

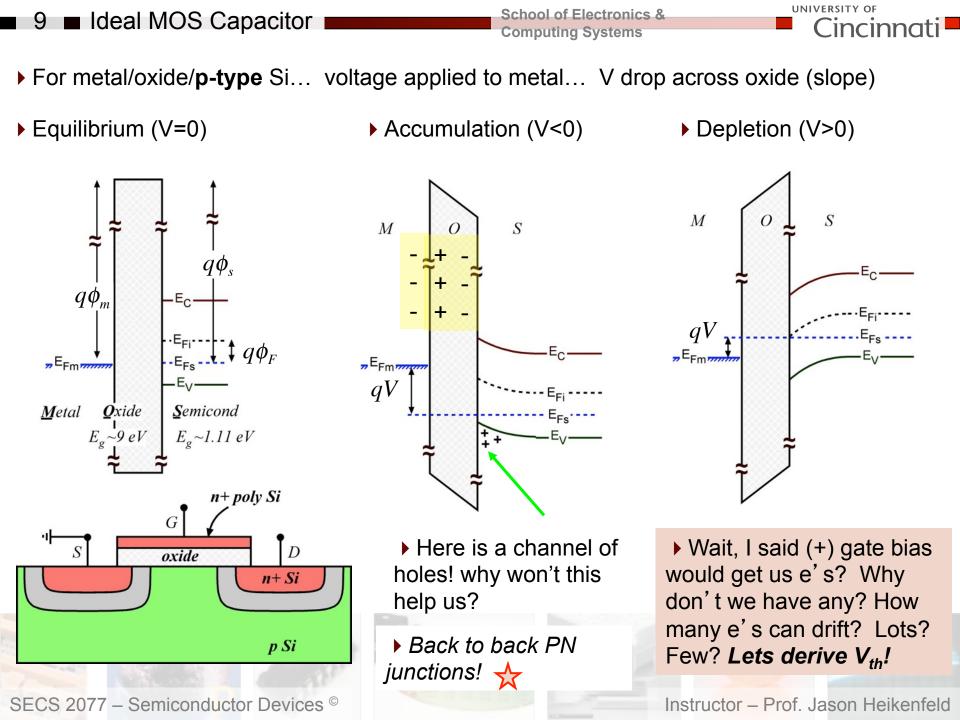

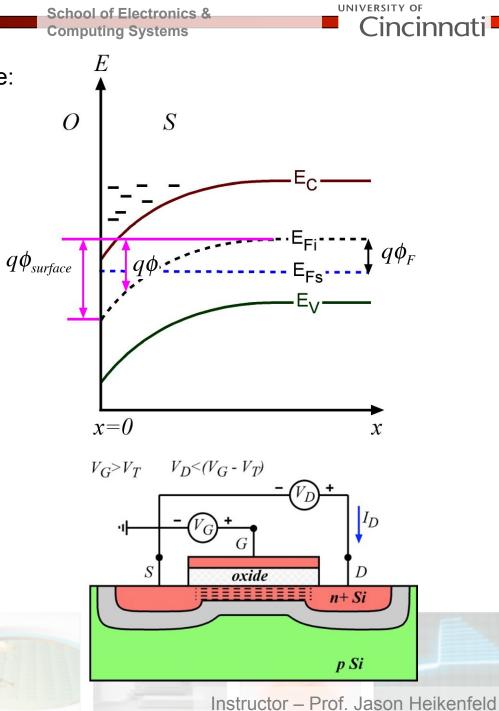

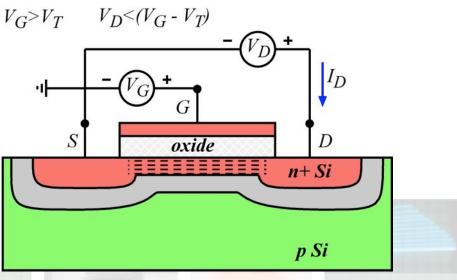

Positive gate voltage (charge) greater than threshold voltage

This requires negative voltage (charge) below gate oxide (capacitor charge up!)

Small drain voltage to allow drift current (no substantial effect on PN junctions)

▶ Electron accumulation (*inversion*) forms a channel through which current can flow, source/drain current is allowed, oxide prevents any gate current...

• Electron accumulation mimics n-type material (hence why called NMOS), so a depletion region is formed outside channel

► This depletion region isolates the device from the substrate (which is good for multidevice integration, VLSI) 6 Basic Operation

School of Electronics & Computing Systems

Cincinnati

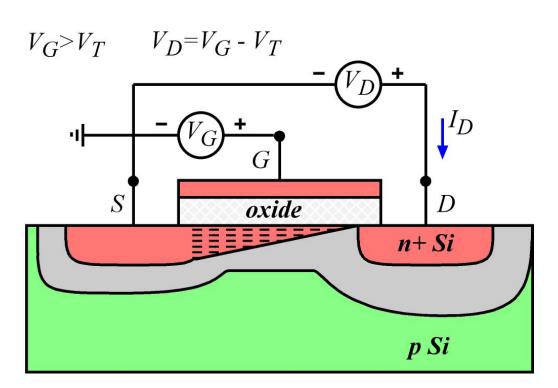

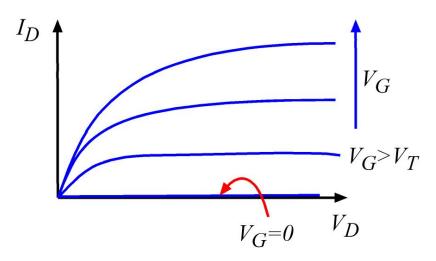

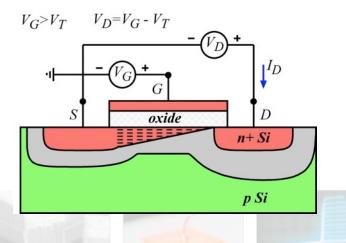

Now we have increased our drain voltage significantly

Like the JFET and MESFET at this point the current flow saturates, what happened?

We can counteract this pinchoff by increasing gate bias

▶ Good animated example: http://www-g.eng.cam.ac.uk/mmg/ teaching/linearcircuits/mosfet.html

- Basic Operation

- Bringing it all together (review)

► We won't spend much time on I(V<sub>d</sub>) or even I(V<sub>g</sub>)! all we care about normally is Vt. <u>why?</u> <u>Think about the applications...</u>

➤ To do this, we need to answer how inversion creates electrons in a p-type material (and we have no current injection, just a capacitor). What has to shift?

Lets derive Vt, hang in there...

SECS 2077 – Semiconductor Devices ©

SECS 2077 – Semiconductor Devices ©

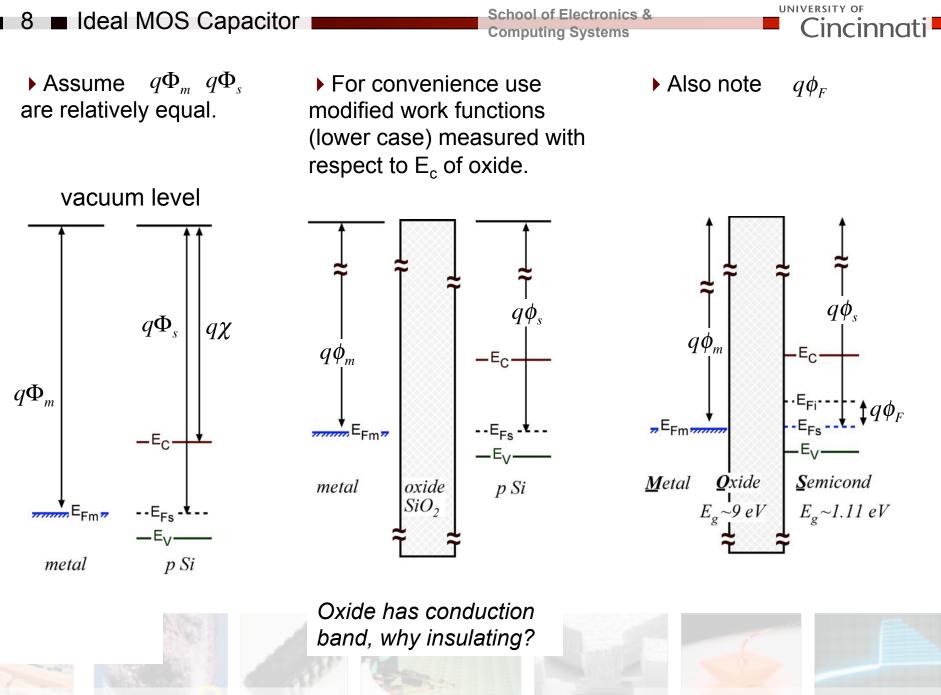

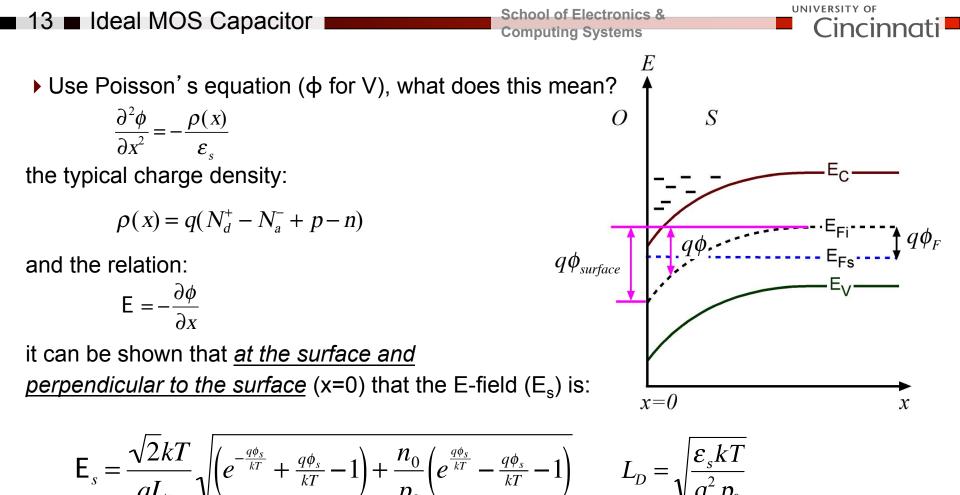

### ■ 10 ■ Ideal MOS Capacitor

School of Electronics & Computing Systems

Depletion (V>0)

### 11 ■ Ideal MOS Capacitor

School of Electronics & Computing Systems Cincinnati

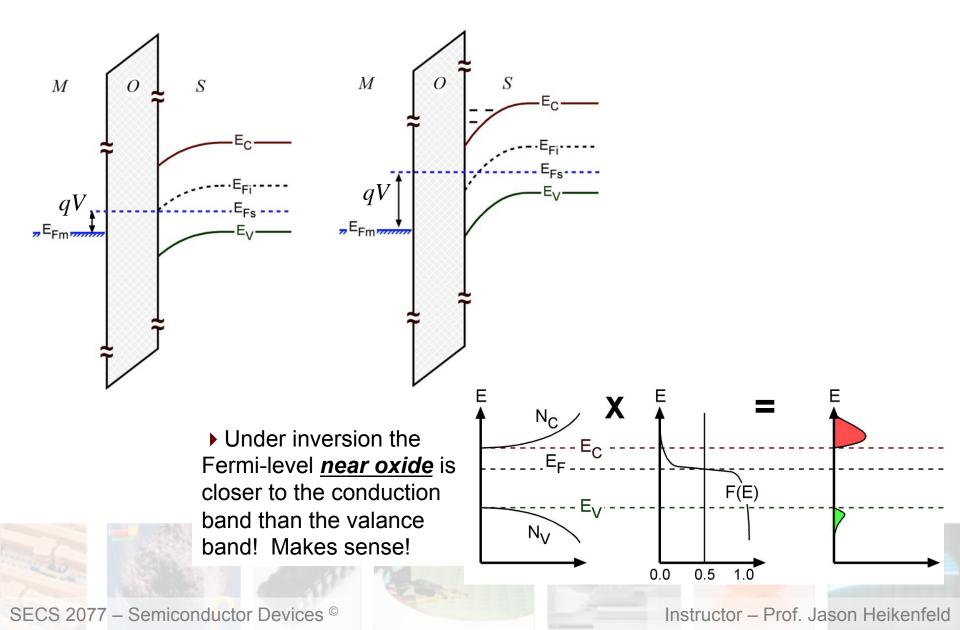

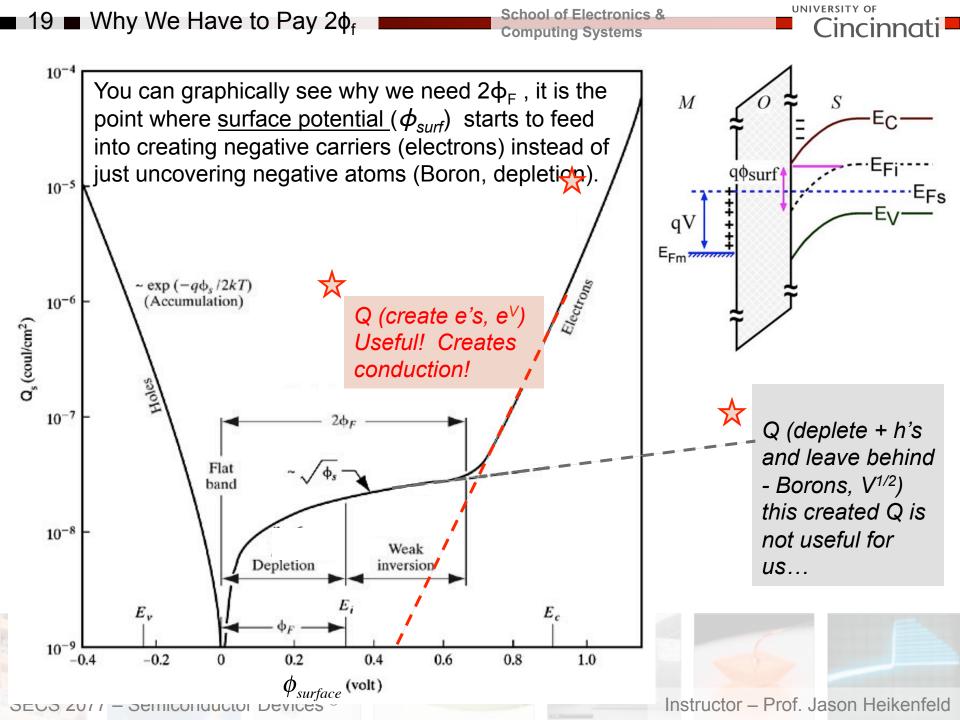

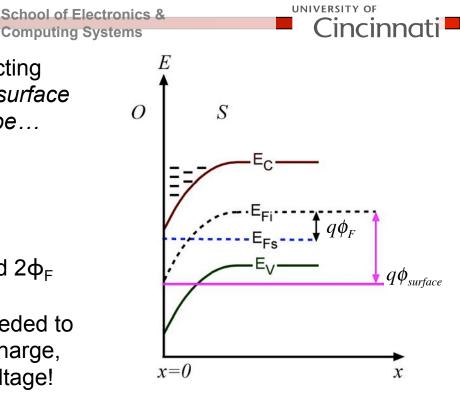

However, to form a true n-type conducting channel (n+) we need to have Strong Inversion

the surface should be just as n-type as it was orginally p-type... (will explain why in a moment)

...  $E_{Fi}$  should be just as far below  $E_{Fs}$  at the surface as it is above  $E_{Fs}$  in the bulk

Another way to put this is that to get strong inversion we need the surface potential ( $\phi_{surface}$ ) to be twice the Fermi offset ( $\phi_F$ ).

$$\phi_{surface}(inv.) > 2\phi_F = 2\frac{kT}{q}\ln\frac{N_a}{n_i}$$

Again, we will see why we need  $2\phi_F$  in a moment...

Hmm.... Surface potential (sounds like it will be part of our threshold voltage). This will also make sense later! Stay tuned!

SECS 2077 – Semiconductor Devices ©

#### 12 ■ Ideal MOS Capacitor

▶ The channel conductivity is based on the electron concentration, lets calculate...

In the bulk:

$$n_0 = n_i e^{(E_f - E_i)/kT}$$

$$= n_i e^{-q\phi_F/kT}$$

As a function of x: qφ

$$n = n_i e^{-q(\phi_f - \phi)/kT}$$

$$= n_i e^{-q\phi_f/kT} e^{q\phi/kT}$$

$$= n_0 e^{q\phi/kT}$$

Same approach for holes...

$$p = p_0 e^{-q\phi/kT}$$

Near surface, what does this tell us for n, p? Device at right I(Vg)?

SECS 2077 – Semiconductor Devices ©

•  $L_{D}$  is the Debye length. It comes up a lot in electrostatics.

We cannot bring all the electrons to x=0, diffusion forces want to push them away.... (look inside the equation, for really heavy doping  $L_D$  is small, why?).

SECS 2077 – Semiconductor Devices ©

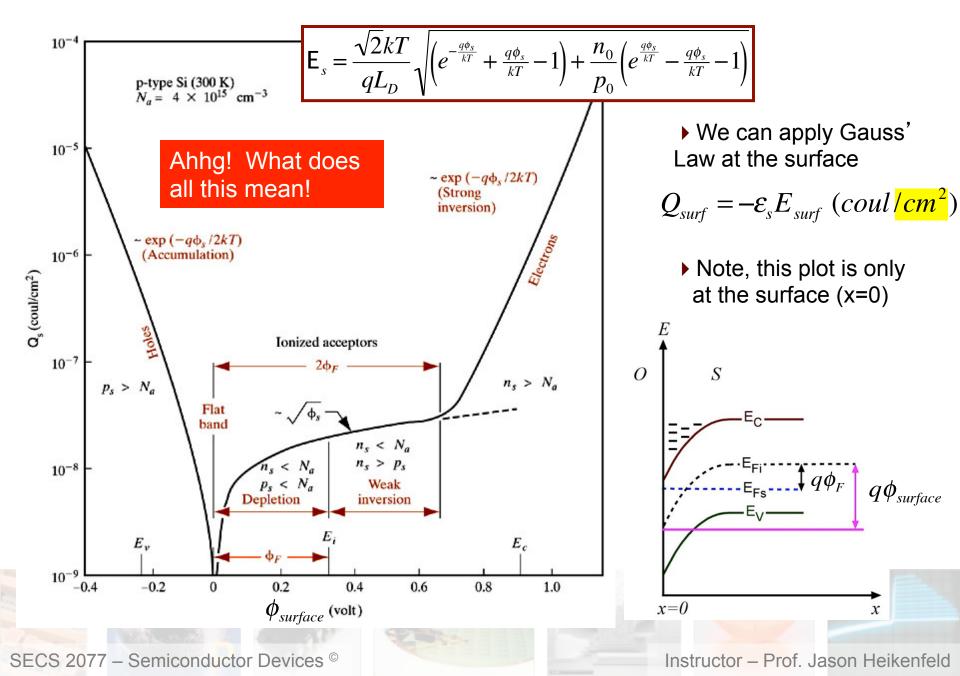

14 ■ Ideal MOS Capacitor

School of Electronics & Computing Systems

## • KEY!!!!

To understand this plot...

- and capacitance vs. voltage,

- and charge distribution vs. voltage,

- and threshold voltage,

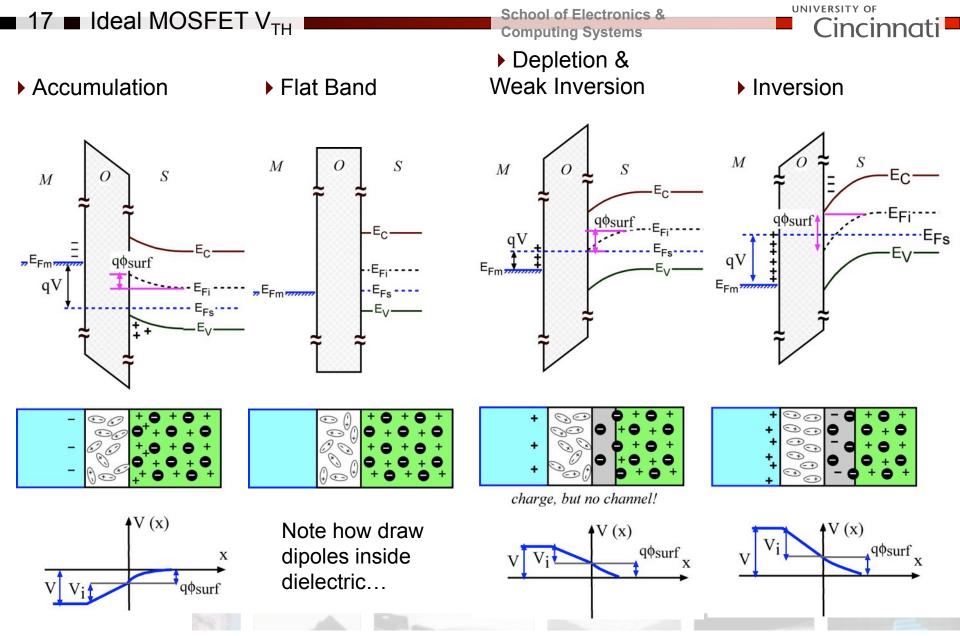

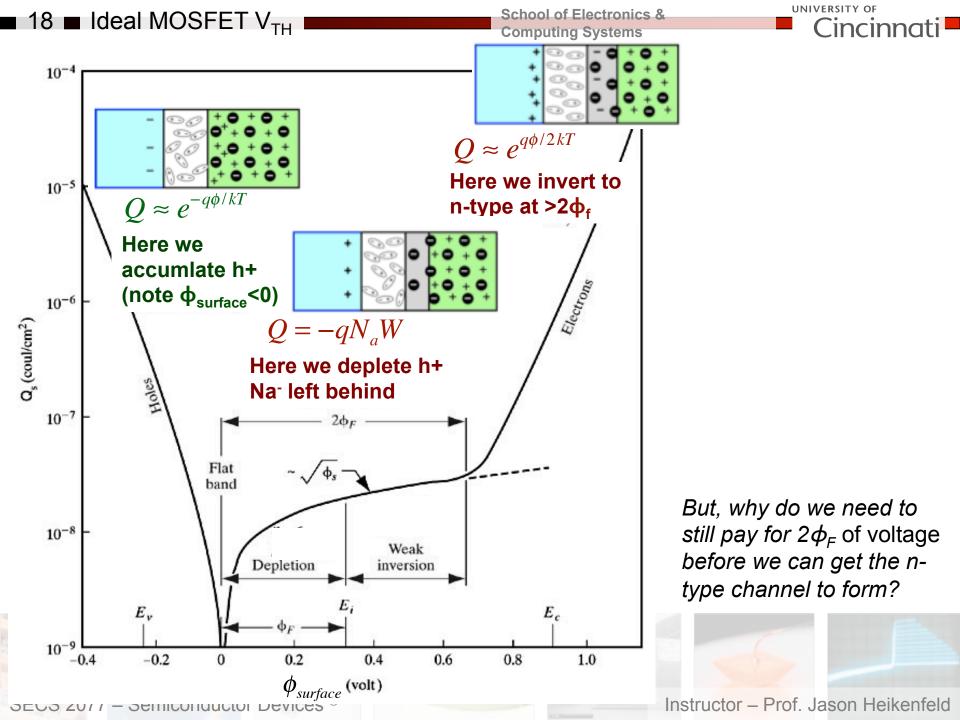

we must understand that there are a series of events that take place in biasing the MOSFET:

Accumulation <-> Flatband <-> Depletion <-> Inversion

You cannot move to one state, without having passed through the other. This will have a large implication on capacitance (switching speed) and theshold voltage!

■ 16 ■ Review! Take a Break!

► Why can't I get current flow from source to drain without gate voltage? No hint needed, answer should be obvious now!

► If I apply negative voltage to the gate what will happen? Why no source-drain current? *Hint:* negative voltage is negative charge on the gate electrode, which on the other side of the capacitor is therefore positive charge (holes).

► If I apply positive voltage to the gate, what happens BEFORE the MOSFET is turned on? *Hint: before* you get electrons (n-type channel), you first get something that still does not allow source-to-drain current, what is it?

► If the MOSFET is on and I keep increasing the source drain voltage, what will happen and why? What type of current flow is this? *Hint, answer with the same terms we used for previous transistors!*

► The MOSFET at right is NMOS, why called NMOS? No hint needed!

SECS 2077 – Semiconductor Devices ©

School of Electronics &

**Computing Systems**

UNIVERSITY OF

incin

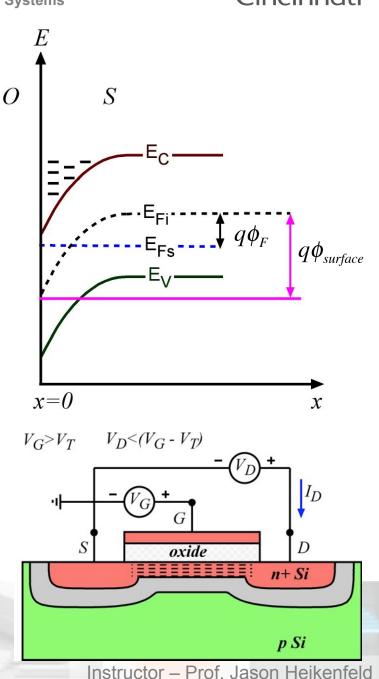

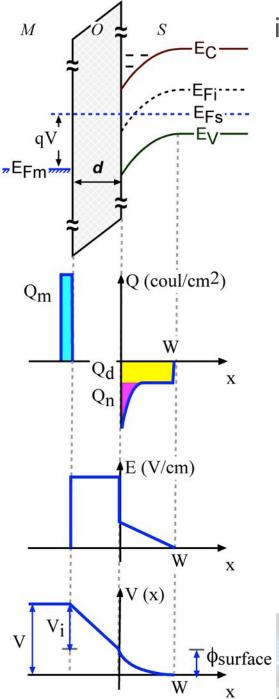

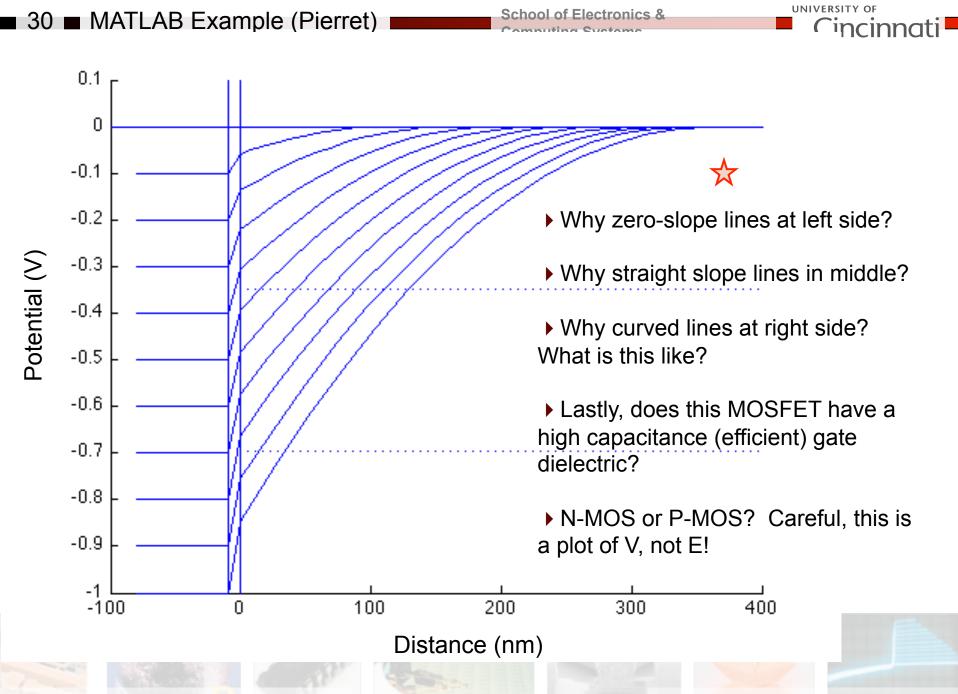

Straight band bend = constant V drop (constant E), curved band = non-constant V drop... Curved for semicon. because contributing charge decreases (and screens) as get toward edge.

SECS 2077 – Semiconductor Devices ©

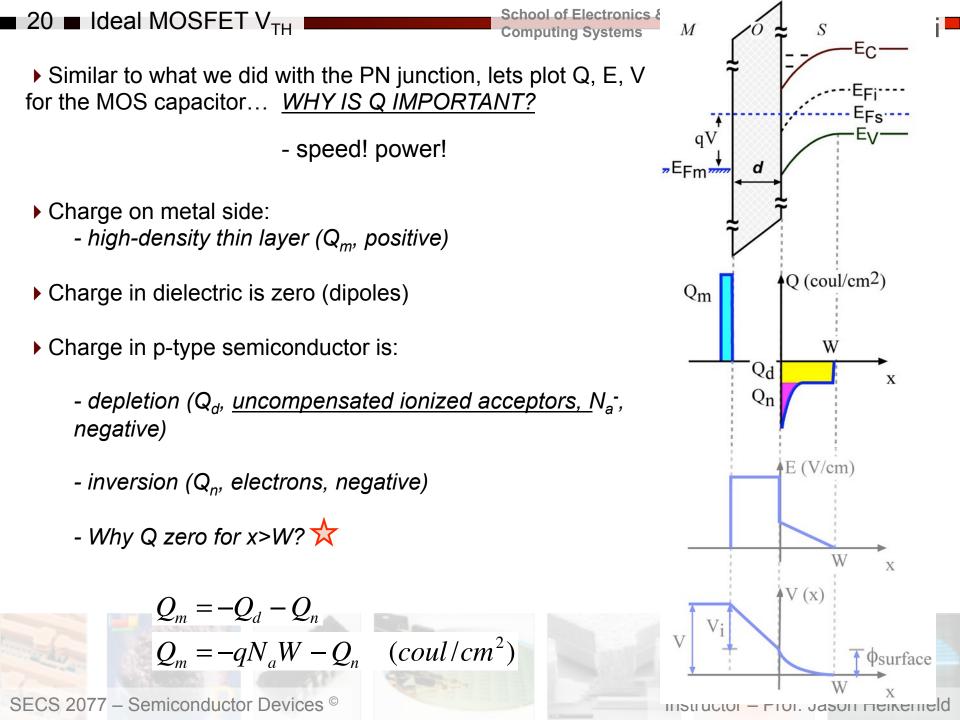

21 ■ Ideal MOSFET V<sub>TH</sub>

Vi is

► Note, channel is exaggerated in figure at right, typically it is only ~10 nm.

• Our applied voltage is split up as voltage across the oxide <u>insulator</u> and the bands (both are sloped, right?!):

$$V = V_i + \phi_{surface}$$

$C = \frac{\varepsilon A}{d}$   $V_i = Q_i / C$

wasted...  $V_i$  will be part of the price we have to pay for  $V_T$

Next, figure out how much depletion we need (we also have to pay with voltage for that too, right?).... we can treat like a n

+p junction and assume all deplete into p-side:

$$W = \left[\frac{2\varepsilon(V_0 - V_{app})}{q} \left(\frac{N_a + N_d}{N_a N_d}\right)\right]^{1/2}$$

$$W = \sqrt{\frac{2\varepsilon_s \phi_{surface}}{qN_a}}$$

Note similarity to Debye Length...

$$L_D = \sqrt{\frac{\varepsilon_s kT}{q^2 p_0}} \quad \frac{kT}{q} = thermal \ volt.$$

School of Electronics &

Computing Systems

M

qV

"EFm

Qm

S

Q (coul/cm<sup>2</sup>)

W

х

Qd

Qn

■ 22 ■ Ideal MOSFET V<sub>TH</sub>

School of Electronics & Computing Systems

▶ Like a PN junction, W increases as we apply more V and further deplete the p-type material...

► However, eventually inversion sets in <u>exponentially</u> and takes over the charge increase as voltage is added...

Therefore depletion region (W) stops growing at a maximum value of:

$W = \sqrt{\frac{2\varepsilon_s \phi_{surface}}{qN_a}} \quad \phi_{surface}(inv.) = 2\phi_F = 2\frac{kT}{q} \ln \frac{N_a}{n_i}$  $W_{m} = \sqrt{\frac{2\varepsilon_{s}\phi_{surface}(inv.)}{aN_{s}}}$ Key point! W  $=2\sqrt{\frac{\varepsilon_{s}kT\ln(N_{a}/n_{i})}{a^{2}N}}$ maximizes! Inversion takes over all the new Q at some point!

SECS 2077 – Semiconductor Devices ©

FIUI. JASULI HEIKELLE

## ■ 23 ■ Ideal MOSFET V<sub>TH</sub>

• We had already shown depletion charge:

$$Q_d = -qN_aW \quad (coul/cm^2)$$

▶ We can substitute W<sub>m</sub> into Q<sub>d</sub>

$$W_m = 2\sqrt{\frac{\varepsilon_s kT \ln(N_a/n_i)}{q^2 N_a}}$$

$$\frac{kT}{q}\ln\frac{N_a}{n_i} = \phi_F$$

And obtain the <u>maximum</u> depletion charge as:

$$Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F} \quad (coul/cm^2)$$

*HOW CAN WE TURN THIS INTO A VOLTAGE?*

SECS 2077 – Semiconductor Devices ©

### 24 ■ Ideal MOSFET V<sub>TH</sub>

• Okay, lets calculate  $V_{TH}$ ! 1<sup>st</sup>, recall for conducting channel we need to have **strong** Inversion, *the surface should be just as n-type as the substrate is p-type...*

$$\phi_{surface}(inv.) > 2\phi_F = 2\frac{kT}{q}\ln\frac{N_a}{n_i}$$

$\blacktriangleright$  To get the threshold voltage we therefore need  $2\varphi_{F}$

• However, before we could achieve  $2\phi_F$  we needed to max out the depletion region, and that creates charge, and using Q=CV means it requires additional voltage!

$$Q_{d,\max} = -2\sqrt{\varepsilon_s q N_a \phi_F} \quad (coul/cm^2)$$

Therefore the 'ideal' case for MOSFET threshold voltage is:

$$V_T = -\frac{Q_{d,\max}}{C_i} + 2\phi_f \qquad C_i = \varepsilon/t$$

SECS 2077 – Semiconductor Devices ©

#### ■ 25 ■ Look Familiar?

School of Electronics & Computing Systems

UNIVERSITY OF

Cincinnati

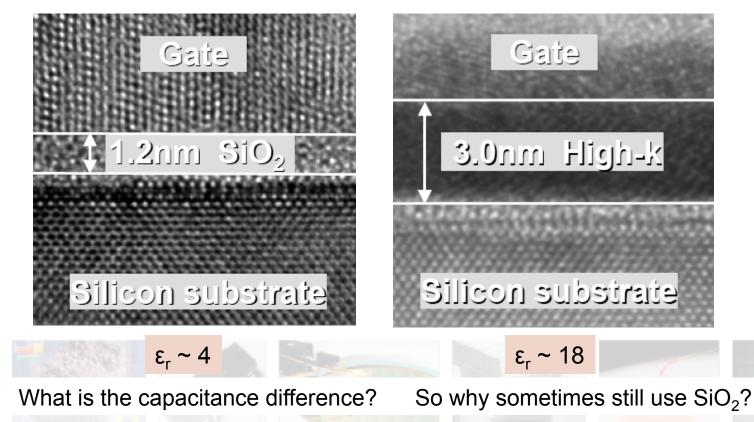

■ 26 ■ Reducing  $V_{TH}$

School of Electronics & Computing Systems

Cincinnati

$$V_T = -\frac{\mathsf{Q}_{d,\max}}{\mathsf{C}_i} + 2\phi_f \qquad C_i = \varepsilon/t$$

There is a limit to decreasing t (oxide thickness)... Why?

▶ Down to a few layers of SiO<sub>2</sub> molecules... chance for defects increases, and <u>tunnel current increases</u>... now using high k ( $\epsilon$ ) HfO<sub>2</sub> etc..

SECS 2077 – Semiconductor Devices ©

28 So many transistor types!

Cincinnati

Instructor – Prof. Jason Heikenfeld

- ▶ How to tell different transistors apart... (but you will find not everyone follows this!).

- So for MOSFETs, why the two parallel lines at the input? Why the 'dot' at the input of PMOS?

- For the JFETs, why no parallel lines and why the arrows at the input?

| ÷¢                               | JFET-N Transistor      | N-channel field effect transistor                           |

|----------------------------------|------------------------|-------------------------------------------------------------|

| ÷¢                               | JFET-P Transistor      | P-channel field effect transistor                           |

| ÷¢                               | NMOS Transistor        | N-channel MOSFET transistor                                 |

| ÷¢                               | PMOS Transistor        | P-channel MOSFET transistor                                 |

| °€¢                              | NPN Bipolar Transistor | Allows current flow when high potential<br>at base (middle) |

| ° $\mathcal{B}_{\mathbf{E}}^{c}$ | PNP Bipolar Transistor | Allows current flow when low potential<br>at base (middle)  |

|                                  |                        |                                                             |

SECS 2077 – Semiconductor Devices ©

## ■ 29 ■ MATLAB Example (Pierret)

School of Electronics & Computing Systems

Cincinnati

#### % Constants

| eps_0 = 8.85e-14 | ; % Units: F/cm   |

|------------------|-------------------|

| kToq = 0.0259    | ; % Units: V      |

| q = 1.6e-19      | ; % Units: C      |

| cm = 1.0e4       | ; % Units: micron |

|                  |                   |

#### % Parameters for Silicon

eps\_si = 11.8 \* eps\_0 ; % Units: F/cm n\_i = 1.5e10 ; % Units: 1/cm^3 N\_a = 1.0e16 ; % Units: 1/cm^3 <--- INPUT DOPING DENSITY

#### % Parameters for Oxide

eps\_ox = 3.9 \* eps\_0 ; % Units: F/cm d\_ox = 10.0 ; % Units: nm <--- INPUT OXIDE THICKNESS

#### Phi\_F = kToq \* log( N\_a/n\_i) ; C\_ox = eps\_ox / (d\_ox \* 1e-7) ; W\_max = 2 \* sqrt( (eps\_si\*Phi\_F) / (q\*N\_a) ) ; Q\_d = q \* N\_a \* W\_max ; V\_T = Q\_d / C\_ox + 2 \* Phi\_F ;

```

W = sqrt( 2*eps_si*V/q/N_a);

```

X\_si = linspace(0,500,51) ; X\_ox = [-10 0] ; X\_m = linspace(-50,-10,5) ; XX = [X\_m X\_si];

axis( [-100 400 -1 .1]); hold on plot( [-100 400] , [ 0 0] ) ; hold on plot( [0 400] , [-Phi\_F -Phi\_F], ':') ; hold on plot( [0 400] , [-2\*Phi\_F -2\*Phi\_F], ':') ; hold on plot( [0 0] , [-1 .1] ) ; plot( [-10 -10] , [-1 .1] ) ;

#### for iV =1:11

Vm = V(iV) ; Vi = V\_ox(iV) ; Vs = V\_si(iV) ; WW = W(iV)\*cm\*1000 + 0.1 ;

xV = linspace(0,WW,15) ; vV = Vs \* (xV/WW - 1) .\* (xV/WW - 1) ;

$\begin{array}{l} plot( \left[ -80 \ -10 \right] \ , \left[ -Vm \ -Vm \right] \ ) \ ; \ hold \ on \\ plot( \ X\_ox \ , \left[ \ -Vs-Vi \ , \ -Vs \right] \ ) \ ; \ hold \ on \\ plot( \ xV \ \ , \ -vV ) \ ; \ hold \ on \end{array}$

end

SECS 2077 – Semiconductor Devices ©

■ 31 ■ Some suggested reading...

School of Electronics & Computing Systems

UNIVERSITY OF Cincinnati

## Last Topic... Who is Andy Grove?

▶ First read 'Only the Paranoid Survive' to appreciate what he accomplished as an Engineer.

▶ Second, read 'Swimming Across' to realize how fortunate you are to be here as an EE.

Third, a business-related book every engineer should read is 'Good to Great'.

Instructor – Prof. Jason Heikenfeld

SECS 2077 – Semiconductor Devices ©

32 ■ Review!

▶ The depletion I can create under the gate oxide maximizes, why? Hint, something else takes over that dominates mathematically in terms of charge generation...

• Once my surface potential is  $(\phi_{surf})$  is above threshold voltage, at what mathematical rate are carriers created in the channel? *Hint: think back to that Qs plot..., think how we calculate carrier concentration*.

Note – we will see next lecture, however, that surface potential and external gate voltage are not proportional...

• Why don't we see strong exponential increase in carriers until the band-bending ( $\phi_s$ ) reaches  $2\phi_F$ ? *Hint: see the Qs plot*

► How does the MOSFET gate voltage change if I reverse all the doping types? No hint needed!

• Why can't I make the oxide thinner and thinner? One word answer will do!

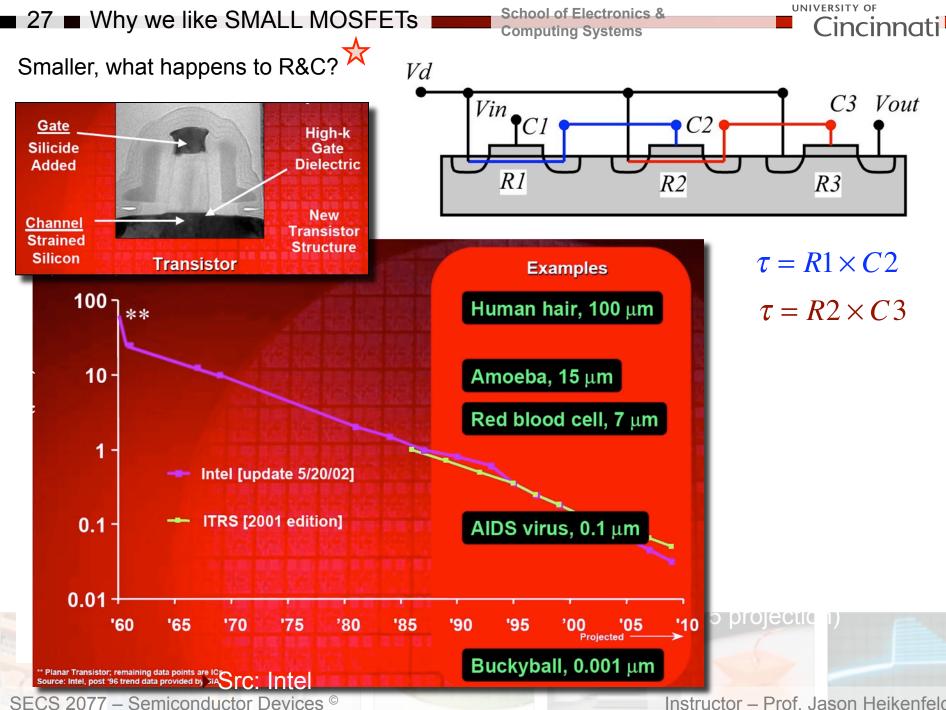

► Why do <u>smaller</u> MOSFETs make faster chips? But remember, more transistors per unit area means more heat generation... which is often the limiter today...